# 74HC595

## Principe de fonctionnement

Le registre à décalage (ou shift register) est un composant électronique contenant des bascules synchrones. Ce sont des circuits logiques qui gardent en mémoire un état haut ou bas (comme un bit) relié par une même horloge. Le principe de décalage vient du fait que l'on vient écrire ou lire dans chaque mémoire bit par bit.

Dans le cas du registre à décalage 74HC595, les sorties parallèles délivreront une tension de 5V à l'état haut et 0V à l'état bas.

- GND masse du circuit intégré

- Vcc broche d'alimentation. Généralement connecté à 5V

- SH\_CP ou RCLK shift register clock input. Le signal d'horloge du registre qui détermine si on écrit dans la mémoire

- ST\_CP ou SRCLK storage register clock input. Le signal d'horloge de stockage qui définit dans quel mémoire on vient lire ou écrire.

- DS ou SER serial data input. Signal contenant la données à enregistrer (HAUT ou BAS)

- Q0-Q7 parallel data output. Broches de sorties du registre à décalage

- OE Output enable, active LOW. Broche connectée à GND pour activer les sorties

- MR Master reset, active LOW. Broche de remise à zéro. Connectée au 5V

- Q7' serial data output (broche utilisée seulement si plusieurs registres sont montés en série)

Le 74HC595 est un registre à décalage qui a les **caractéristiques suivantes** :

- 8 sorties

- courant maximal **par sortie 35mA**

- courant maximal pour l'**ensemble des sorties 70mA**

- Il est possible de chaîner plusieurs 74HC595 pour obtenir un **registre à décalage 16bits, 24bits, 32bits ou plus.**

| Symbol / Parameter                    | Pins         | Test Conditions | Vcc  | TA = +25°C |     |     | -40°C to +85°C |     | -40°C to +125°C |     | Unit |

|---------------------------------------|--------------|-----------------|------|------------|-----|-----|----------------|-----|-----------------|-----|------|

|                                       |              |                 |      | Min        | Typ | Max | Min            | Max | Min             | Max |      |

| f <sub>MAX</sub><br>Maximum Frequency | SHCP or STCP | Figure 1        | 2.0V | 9          | 30  | —   | 4.8            | —   | 4               | —   | MHz  |

|                                       |              |                 | 4.5V | 30         | 91  | —   | 24             | —   | 20              | —   |      |

|                                       |              |                 | 6.0V | 35         | 108 | —   | 28             | —   | 24              | —   |      |

## Principe de fonctionnement du 74HC595:

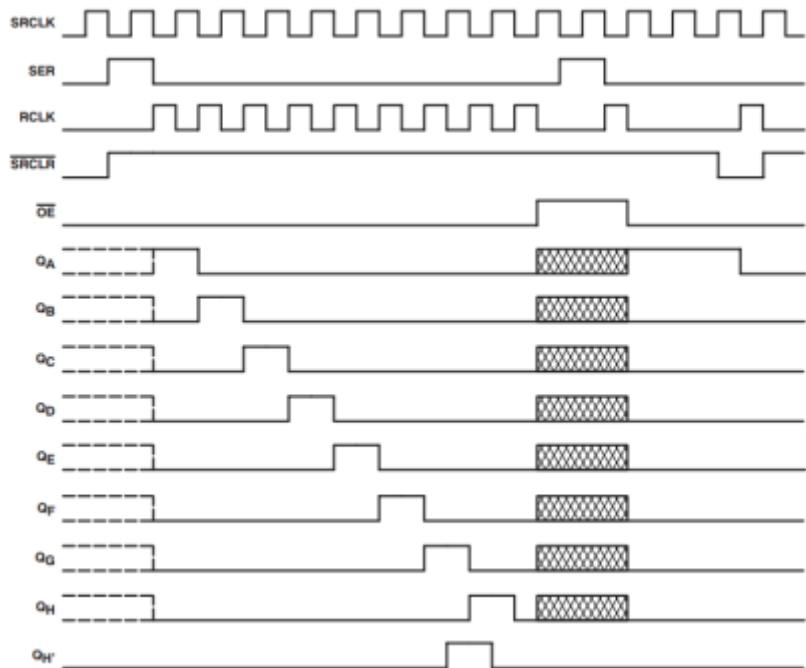

Séquence de fonctionnement pour l'envoie d'une donnée sur 8 bits;

1. - Premièrement, on passe la pin12 (RCLK) à l'état "0".

2. - On présente un à un les 8 bits de la donnée sur la pin14 (SER), tout en envoyant au même moment à chaque bit un état "1" sur la pin11 (SRCLK).

3. - On repasse ensuite la pin12 (RCLK) à l'état "1" pour ainsi recopier la nouvelle valeur dans le second registre.

- La pin10 (SRCLR) a pour fonction de remettre tout le premier registre à zéro (active à l'état "0").

- La pin13 (OE) a pour fonction d'activer ou non la sortie (active à l'état "0").

On peut facilement observer sur le chronogramme que toutes les sorties sont décalées d'un cycle d'horloge à chaque fois par rapport à la sortie qui la précède.

## Programmes pour arduino et 74HC595

[programmes arduino pour 74HC595](#)

## Quelques lien utiles :

<https://learn.adafruit.com/adafruit-arduino-lesson-4-eight-leds/the-74hc595-shift-register>

<https://eskimon.fr/tuto-arduino-901-ajouter-des-sorties-num%C3%A9riques-%C3%A0-larduino-le-74hc595>

[Registre à décalage 74HC595](#)

## 74HC595

Fonctionnement d'un 74HC595

[DataSheet - Doc technique 74HC595 EN](#)

[74HC595 sur Tinkercad](#)

[Fichiers exercices 74HC595](#)

From:

<https://magenealogie.chanterie37.fr/www/fablab37110/> - Castel'Lab le Fablab MJC de Château-Renault

Permanent link:

<https://magenealogie.chanterie37.fr/www/fablab37110/doku.php?id=start:arduino:74hc595&rev=1646734949>

Last update: **2023/01/27 16:08**